Наконец, нам осталось посмотреть на виновника торжества – знаменитую ECL-логику, на которой собирали «Эльбрус-2» и с которой в Союзе были такие адские мучения.

Идея эмиттерно-связной логики довольно проста.

DTL и TTL-логику сложно разогнать до больших частот из-за того, что транзисторы в цикле работы достигают режима насыщения, из которого сравнительно медленно выходят.

В результате родилась идея создания схемы, в которой при переключениях транзисторы оставались бы в линейном режиме.

Так они смогут, грубо говоря, включаться не до конца и очень быстро переключать пути прохождения тока.

Естественно, это приводило к тому, что разница между логическими уровнями была очень низкой по меркам биполярной логики (порядка 0,8В, в 3–4 раза меньше TTL) и схема становилась очень чувствительна к шумам и к нагреву, их порождающему (беда была в том, что благодаря реализации самой идеи грелась схема не по-детски).

Переключение уровня на каждый 1В обычно требует порядка наносекунды, поэтому TTL так тяжело разогнать до скорости, большей, чем 3–4 нс, а для ECL 1–2 нс – это чуть ли не режим работы из коробки без дополнительных ухищрений (только вот в схеме из коробки без ухищрений все сожрут шумы).

Что такое ECL?

Оставить ключ в линейном режиме можно, использовав не просто усиливающий транзистор, а полноценный дифференциальный усилитель.

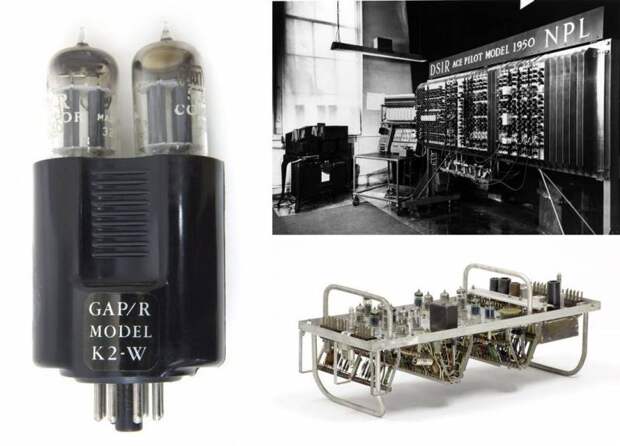

Что забавно, ECL тоже имеет вакуумного предка, так как провернуть такой трюк возможно и с парой ламп. Схему, позже названную длиннохвостой (long-tailed) или дифференциальной (differential, от слова «разность») парой, придумали в Британии, в 1934 году идею опубликовал изобретатель-любитель Брайан Мэтью (Bryan Matthews), и в 1936 году патент подал электроинженер Алан Блюмлейн (Alan Dower Blumlein).

К концу 1930-х топология дифференциальных усилителей была хорошо изучена, а в компьютерах эту прото-ECL впервые применили тоже британцы, EDSAC (University of Cambridge Mathematical Laboratory, 1948), Pilot ACE (National Physical Laboratory, 1950) и несколько других ранних машин, созданных коллегами Блюмлейна, были собраны на дифференциальных ламповых усилителях.

Эта схема имеет много преимуществ в качестве ключа: практически невосприимчива к колебаниям ламп (что важно, если в вашей схеме их тысячи!), высокий коэффициент усиления и его стабильность, высокий входной импеданс, средний/низкий выходной импеданс.

В общем и целом вопросом времени было, когда эту схему приспособят к транзисторам.

Отметим, что мы описали лишь простейший дифференциальный усилитель, в электротехнике это настолько же фундаментальная схема, как какой-нибудь элемент NOR или XOR в электронике. Классическим видом ДУ является операционный усилитель, применяемый повсеместно, от аналоговых компьютеров до стереосистем.

GAP/R Vacuum Tube K2-W Operational Amplifier, изобретенный Джорджем Филбруком (George Philbrick) в 1952 году, стал классикой и использовался во многих аналоговых и цифровых компьютерах. Pilot ACE, построенный Аланом Тьюрингом на дифференциальных усилителях в 1950 году. Блок АЛУ от DEUCE – серийной версии Pilot ACE, построенной в 1955 году English Electric Company. 32-битный DEUCE осуществлял 1850 сложений в секунду. (https://www.computerhistory.org)

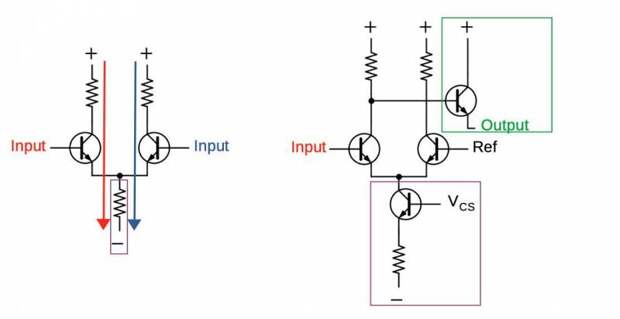

Работает дифференциальный усилитель достаточно просто.

Через схему с двумя плечами проходит фиксированный ток. Если напряжение на левом входе больше, чем на правом, включается левый транзистор, и большая часть тока пойдёт через левое ответвление, и наоборот.

Небольшая разница между входящими сигналами порождает большое изменение тока, отсюда и усилитель.

Добавлением пары транзисторов мы легко получаем из усилителя вентиль. Для этого надо зафиксировать напряжение в одном из плечей, поименовав его опорным. Если входящий сигнал больше опорного, он считается «1», а если ниже – «0». Как повелось еще с IBM, обычно в качестве опорного используется уровень земли.

В результате мы имеем очень-очень быструю схему, неустойчивую к помехам, жрущую много энергии и аналогично греющуюся. Из-за последних двух причин сложно повышать уровень интеграции ECL-микросхем – пара миллиардов транзисторов на CMOS будут греться меньше и занимать меньше места, чем 50 тысяч ECL.

Преодолению этих ограничений и были посвящены работы компаний Motorola и Fairchild.

Дифференциальный усилитель и инвертор на его основе. Если входящий сигнал высокий, ток через левый резистор подтянет напряжение вниз. Для увеличения быстродействия нижний резистор заменён на сток тока (фиолетовый). Ток через сток управляется внешним напряжением смещения. К выходу добавлен буфер (зелёный). Буфер называется эмиттерным повторителем, поскольку выход берётся с эмиттера транзистора, а выход повторяет вход (схема из блога Кена Ширриффа).

Первым компьютером, собранным на ECL, стал, как мы уже и говорили, могучий IBM 7030 Stretch, собственно, для него она и разрабатывалась.

IBM хотела выпустить настоящего исполина, превосходящего самые быстрые компьютеры на тот момент раз в 10–12, естественно, никакая уже известная схемотехника для этого не подходила.

Инновацией Stretch стала эмиттерно-связная логика, созданная инженером IBM Ханноном Юрке (Hannon S. Yourke). Переключатель Юрке представлял собой дифференциальный усилитель с двумя логическими опорными уровнями напряжением 3 вольта и требовал чередования двух npn и pnp-каскадов.

Эта схема использовалась не только в 7030, но и в научном 7090, и позже – воплощенная в виде ГИС в суперкомпьютере для NASA System 360 model 91.

К началу 1960-х было разработано множество схем эмиттерно-связной логики, включая варианты с диодами Зенера, позволяющими обойтись без 2 видов транзисторов.

Версия IBM для S/370 (а они не экономили и во второй линейке мейнфреймов использовали ECL буквально везде), воплощенная в виде микросхемы, назвалась CSEF (Current-Switch Emitter Follower).

Оригинальная схема Юрке, использовавшаяся в IBM 7030 Stretch, ASLT-микросхема IBM 360/91 (J. L. Langdon, E. J. Vanderveer, Design of a High-Speed Transistor for the ASLT Current Switch, 1967) и базовая ячейка Motorola 10k.

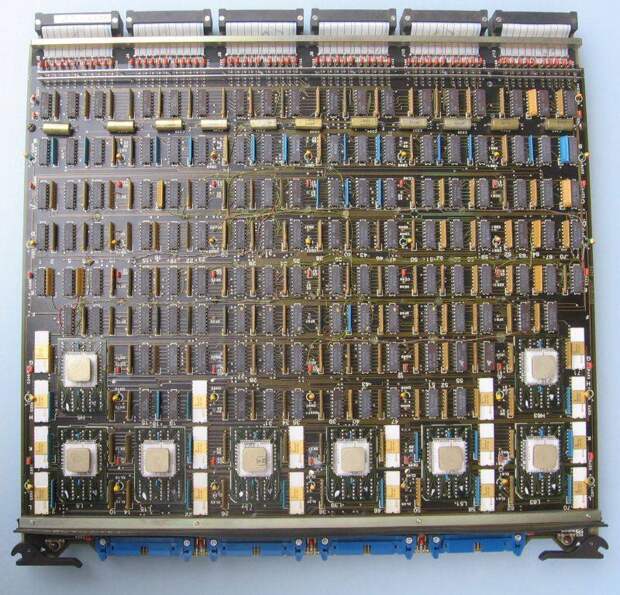

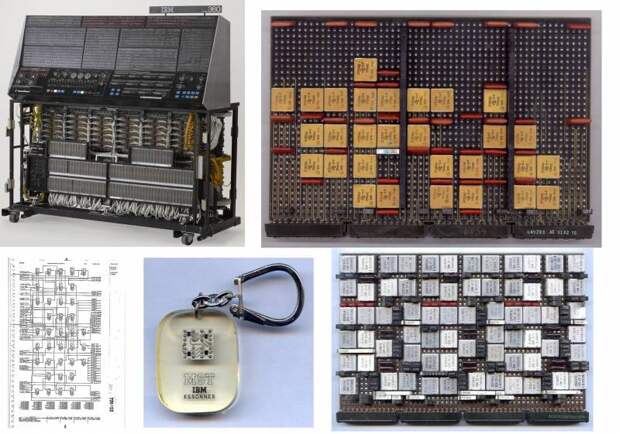

Сверху: чудовищная консоль суперкомпьютера IBM System/360 Model 195. При стоимости инсталляции 12,5 миллионов долларов и дополнительной цене техподдержки в 3,3 миллиона в год это был самый дорогой компьютер тех лет. Будучи прямым конкурентом CDC 7600, выполненный на фирменных ECL-микросхемах, Model 195 превосходил его в мощности, но был изготвлен позднее и не пользовался популярностью (за 1971–1977 вышло всего 20 машин, против 200 – у CDC). Одна карта от Model 195. Обратите внимание на чипы – они изготовлены Texas Instruments, это был единственный случай в истории, когда IBM обратилась за помощью в выпуске к сторонней компании! Корпуса тоже удивляют – позолоченные, металлокерамические. Каждая ИС содержит от 2 до 4 вентилей, обычно двухвходовых NAND. Время переключения вентилей составляло около 3 нс.

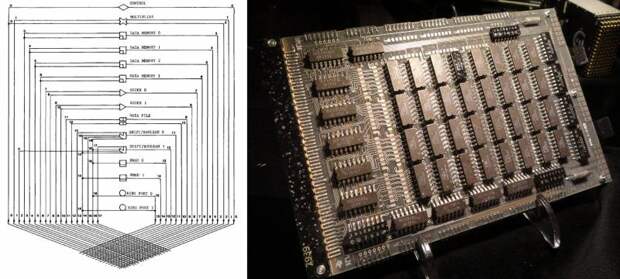

Снизу: логическая диаграмма ALD (Automated Logic Diagram), созданная программным обеспечением IBM EDA (Electronic Design Automation) автоматизированного проектирования логических схем. Фирменный брелок с MST-чипом, явно видны 4 кристалла ИС. MST-карта процессора мейнфрейма IBM System/370 model 145 1982 года. Каждый чип на ней содержал до 5 ECL-микросхем и заменял целую плату от S/360. Практически по тому же пути попытались двинуться советские копировщики из НИЦЭВТ в 1980-е, заменить одним БМК целый ТЭЗ

(http://ibm-1401.info, http://ummr.altervista.org/).

Снизу: логическая диаграмма ALD (Automated Logic Diagram), созданная программным обеспечением IBM EDA (Electronic Design Automation) автоматизированного проектирования логических схем. Фирменный брелок с MST-чипом, явно видны 4 кристалла ИС. MST-карта процессора мейнфрейма IBM System/370 model 145 1982 года. Каждый чип на ней содержал до 5 ECL-микросхем и заменял целую плату от S/360. Практически по тому же пути попытались двинуться советские копировщики из НИЦЭВТ в 1980-е, заменить одним БМК целый ТЭЗ

(http://ibm-1401.info, http://ummr.altervista.org/).

Советским ответом на IBM 7030 стала БЭСМ-6, собранная на довольно изысканном варианте ECL.

Проблема перед разработчиками стояла, в общем-то, та же: увеличить быстродействие, не чрезмерно усложняя схему, но была одна специфическая особенность – убожество отечественной элементной базы.

В середине 60-х советская промышленность умела выпускать только два быстрых полупроводниковых прибора: диод Д18 и транзистор П416. Да и те были довольно плохого качества. Пришлось изобретать хитрую схемотехнику.

Суть описывает один из конструкторов БЭСМ-6 В. Н. Лаут:

Промышленность выпускала дискретные германиевые диоды и триоды с весьма плохими характеристиками.

Можно ли на них было разработать элементы для высокопроизводительной машины?

…К этому времени в специальной литературе появилось много сообщений об использовании в качестве основы для схем быстродействующей логики туннельных диодов. Эти диоды имели малые времена переключения, во много раз лучшие, чем у транзисторов.

Однако элементы на туннельных диодах получились с плохой нагрузочной способностью, что приводило к усложнению схем машины, и довольно быстро мы от них отказались…

Трудность с использованием транзисторов заключалась в том, что в режиме насыщения они работали очень медленно, а логические элементы с ненасыщенными триодами получались сложными из-за необходимости согласования уровней входных и выходных сигналов.

И не только сложными, но и ненадежными.

Некоторое время мы не видели выхода из тупика.

Можно ли на них было разработать элементы для высокопроизводительной машины?

…К этому времени в специальной литературе появилось много сообщений об использовании в качестве основы для схем быстродействующей логики туннельных диодов. Эти диоды имели малые времена переключения, во много раз лучшие, чем у транзисторов.

Однако элементы на туннельных диодах получились с плохой нагрузочной способностью, что приводило к усложнению схем машины, и довольно быстро мы от них отказались…

Трудность с использованием транзисторов заключалась в том, что в режиме насыщения они работали очень медленно, а логические элементы с ненасыщенными триодами получались сложными из-за необходимости согласования уровней входных и выходных сигналов.

И не только сложными, но и ненадежными.

Некоторое время мы не видели выхода из тупика.

Нужна была схема питания, минимизирующая количество ненадежных транзисторов, и ключевой ее элемент придумал тот самый Соколов, который позже собирал МКП для Бурцева (а коллектив БЭСМ-6 раскололся после смерти Лебедева, последовав за Мельниковым или Бурцевым).

Суть идеи заключалась в том, чтобы в известный элемент «токовый переключатель» ввести автономный источник питания, гальванически не связанный с другими цепями питания.

Например, для этой цели можно было бы использовать миниатюрную батарейку от электронных часов.

Включение батарейки между коллектором транзистора и коллекторной нагрузкой (резистором) делало переключатель элементом с согласованными уровнями входных и выходных сигналов, причем к автономному источнику питания не предъявлялось особенно сложных требований.

Конечно, батарейку ставить было нельзя, так как она со временем разрядится, поэтому в реальной схеме ее заменил крошечный выпрямитель, состоящий из миниатюрного трансформатора на ферритовом кольце, двух полупроводниковых диодов и конденсатора.

Назвали эти выпрямители «подвешенными источниками питания» (ПИП).

Парафазные выходы переключателей тока, снабженные эмиттерными повторителями, могли работать на входы логических схем «И», «ИЛИ».

Вырисовывалась такая схемотехника: пассивная комбинаторная логика на диодно-резисторных компонентах подключалась к входам усилительных активных элементов, выходы которых, в свою очередь, соединялись с входами комбинаторных схем и т.д.

Таким образом, электронное тело машины выглядело как слоеный пирог: слои диодных логических схем перемежались слоями усилителей на переключателях тока.

Такая структура очень подходила для осуществления другой чрезвычайно мощной идеи – «конвейерной работы».

Для этого на вход усилителей, выполняющих функции триггеров, завели еще сигналы синхронизации.

Конвейерная схемотехника с легкой руки Сергея Алексеевича Лебедева стала называться у нас «водопроводом».

БЭСМ-6 стала первой советской машиной, в которой использовалась конвейерная работа. Темп конвейера, определяемый частотой сигналов синхронизации, в БЭСМ-6 был равен 10 МГц.

Итак, была разработана совершенно новая система логических элементов, позволяющая выжать максимум быстродействия из имеющихся не слишком качественных отечественных транзисторов и диодов.

Затем возникла необходимость в разработке конструкции такой машины, чтобы не потерять потенциального быстродействия логических элементов, а также технологичной и удобной в эксплуатации.

В 50-х годах еще не было многослойных печатных плат, широко используемых в конструкциях современных ЭВМ.

В БЭСМ-6 печатные платы (двусторонние) применялись только в ячейках (ТЭЗах), которые были двух типов: с активными элементами-триггерами и пассивными комбинаторными схемами.

Активные ячейки имели на торцах световые индикаторы и устанавливались с лицевой стороны стоек, образуя своеобразное световое табло, с тыльной стороны стоек размещались пассивные ячейки.

Объемные объединительные панели имели разъемы с двух сторон, а проводные связи проходили внутри между разъемами по кратчайшему пути.

Это была необычная конструкция. Она уменьшала размеры машины, а, следовательно, и времена пробега сигналов.

Например, для этой цели можно было бы использовать миниатюрную батарейку от электронных часов.

Включение батарейки между коллектором транзистора и коллекторной нагрузкой (резистором) делало переключатель элементом с согласованными уровнями входных и выходных сигналов, причем к автономному источнику питания не предъявлялось особенно сложных требований.

Конечно, батарейку ставить было нельзя, так как она со временем разрядится, поэтому в реальной схеме ее заменил крошечный выпрямитель, состоящий из миниатюрного трансформатора на ферритовом кольце, двух полупроводниковых диодов и конденсатора.

Назвали эти выпрямители «подвешенными источниками питания» (ПИП).

Парафазные выходы переключателей тока, снабженные эмиттерными повторителями, могли работать на входы логических схем «И», «ИЛИ».

Вырисовывалась такая схемотехника: пассивная комбинаторная логика на диодно-резисторных компонентах подключалась к входам усилительных активных элементов, выходы которых, в свою очередь, соединялись с входами комбинаторных схем и т.д.

Таким образом, электронное тело машины выглядело как слоеный пирог: слои диодных логических схем перемежались слоями усилителей на переключателях тока.

Такая структура очень подходила для осуществления другой чрезвычайно мощной идеи – «конвейерной работы».

Для этого на вход усилителей, выполняющих функции триггеров, завели еще сигналы синхронизации.

Конвейерная схемотехника с легкой руки Сергея Алексеевича Лебедева стала называться у нас «водопроводом».

БЭСМ-6 стала первой советской машиной, в которой использовалась конвейерная работа. Темп конвейера, определяемый частотой сигналов синхронизации, в БЭСМ-6 был равен 10 МГц.

Итак, была разработана совершенно новая система логических элементов, позволяющая выжать максимум быстродействия из имеющихся не слишком качественных отечественных транзисторов и диодов.

Затем возникла необходимость в разработке конструкции такой машины, чтобы не потерять потенциального быстродействия логических элементов, а также технологичной и удобной в эксплуатации.

В 50-х годах еще не было многослойных печатных плат, широко используемых в конструкциях современных ЭВМ.

В БЭСМ-6 печатные платы (двусторонние) применялись только в ячейках (ТЭЗах), которые были двух типов: с активными элементами-триггерами и пассивными комбинаторными схемами.

Активные ячейки имели на торцах световые индикаторы и устанавливались с лицевой стороны стоек, образуя своеобразное световое табло, с тыльной стороны стоек размещались пассивные ячейки.

Объемные объединительные панели имели разъемы с двух сторон, а проводные связи проходили внутри между разъемами по кратчайшему пути.

Это была необычная конструкция. Она уменьшала размеры машины, а, следовательно, и времена пробега сигналов.

В общем, это была, наверное, самая экстравагантная схема реализации ECL с необычным источником питания из всех возможных.

Стандартная плата, так называемый модуль «У», из которых и собирался процессор (четыре асинхронных RS-защёлки), требовала аж шести номиналов питания: +40 В, +5 В, –1,6 В, –3,5 В, –9 В, –60 В, не считая переменных 6 В на вход подвешенного источника питания (ПИП) – это сущая дичь даже по меркам начала 1960-х, не говоря уже о 1968 или сегодняшних временах.

Технически логика в БЭСМ-6 была действительно реализована на диодах, так что в итоге получилось нечто среднее между DTL и ECL.

Отдельным бонусом было то, что работало все на воздухе – для CDC 6600 потребовался фреон, и это было очень сложно и слишком дорого.

Сама система охлаждения машины весила больше 7 тонн и занимала отдельное помещение (вместе с питанием). В БЭСМ-6 обошлись без таких извращений, тем более что толково работать с фреоном в СССР не умели даже в конце 1980-х (сколько намучались с охлаждением «Электроника ССБИС», расскажем позднее).

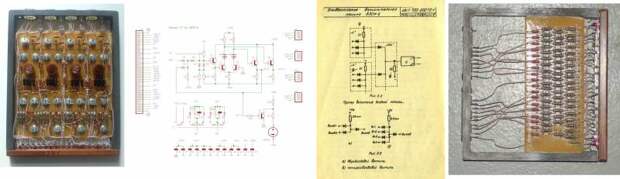

Блок «У» – основа БЭСМ, его современная схема, комбинаторные схемы, куда он подключался, и их воплощение в железе (https://1500py470.livejournal.com)

Как видите, идея была неплохая, при этом формально частота была достигнута та же, что и в CDC 6600 – 10 МГц (впрочем, это со слов, какова была реальная и у самых первых версий БЭСМ-6, чисто транзисторных, неизвестно).

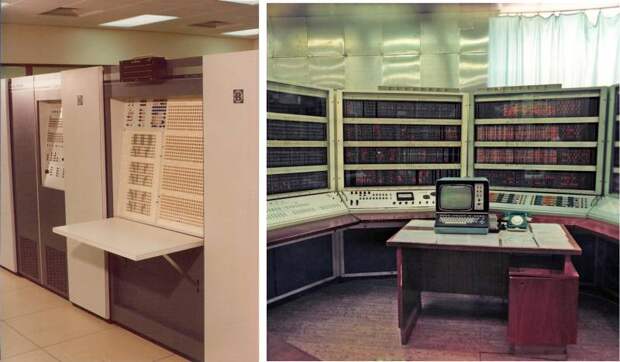

Системная архитектура – в виде подковы, уменьшающей длину соединений и делающей удобным управление, тоже была очень хорошей идеей, да и выглядела БЭСМ-6 не хуже CDC.

Управление, впрочем, было реализовано максимально небанально – ИТМиВТ по каким-то сакральным причинам не любил инженерные пульты, традиционные для машин 50–60-х годов (а для больших машин – так и до 1970-х). Как правило, вся индикация и прочее выводились в ЭВМ на отдельную консоль.

В БЭСМ-6 же, по сути, весь процессор и был одновременно консолью, лампочки были выведены на каждый ТЭЗ и бодро мигали в процессе работы!

Кстати, надо пояснить, что это вообще такое.

Инженерный пульт не стоит путать с терминалом, за терминалами работали программисты-пользователи машины. А на пульт выводилась физическая информация о текущих операциях процессора, содержимое всех регистров и т. п. При этом в большинстве случаев ее можно было изменять вручную.

Делались такие пульты не от хорошей жизни, а потому, что старые машины требовали отладки и постоянного контроля в процессе выполнения программы.

Кстати, на отсутствие такового пульта в штатной комплектации «Эльбрус-1» в 1980-е жаловались многие пользователи.

Традиционный инженерный пульт Burroughs B6700 и пульт-процессор БЭСМ-6

(http://www.retrocomputingtasmania.com, https://vak.dreamwidth.org/)

(http://www.retrocomputingtasmania.com, https://vak.dreamwidth.org/)

Однако производительность машины все равно оказалась ниже в 2,5 раза, а надежность – в 1,5 раза меньше.

В чем же причина?

Отчасти, действительно, советская элементная база (хотя по сравнению с первым поколение микросхем 155-й серии в ЕС Ряд-1 советские транзисторы в БЭСМ-6, можно сказать, были абсолютно надежными).

Основная же проблема была в системной архитектуре.

Единственное, к чему приложил руку Лебедев в этой машине – это придумал ее систему команд, и она оказалась настолько кривой, что, как мы позже узнаем, даже точная реализация БЭСМ-6 на невероятно быстрых микросхемах И200 (ECL БМК) не позволила поднять производительность даже в 10 раз (хотя в теории должна была поднять раз в тридцать).

Даже микропроцессорная реализация чудовищной лебедевской системы команд родом из начала 1950-х годов вряд ли выжала из БЭСМ-6 больше, чем захудалый 386 процессор. Все-таки элементная база – это еще далеко не все, архитектура команд играет большую роль, которую никогда не могла правильно оценить лебедевская школа.

Что касается ее главного конкурента – CDC 6600, то Крэй использовал в машине тоже достаточно экзотический вариант – транзисторную логику с прямой связью (direct-coupled transistor logic, DCTL), что-то среднее между TTL и RTL.

DCTL-затворы имеют меньше компонентов, более экономичны и проще в изготовлении на интегральных схемах, чем RTL-затворы, а еще они на порядок быстрее. К сожалению, DCTL имеет гораздо меньший уровень сигнала, более восприимчив к шуму и требует согласованных характеристик транзисторов, потому что они сильно перегружены. Это хорошая особенность, поскольку она снижает напряжение насыщения выходных транзисторов, но в случае несогласованных элементов она может замедлить схему.

Работает она очень быстро (даже быстрее ECL!), при этом греется настолько чудовищно, что Крэю уже в 1966 году понадобился фреон, чтобы его машина не расплавилась.

В случае DCTL разница между логическими уровнями настолько низка (а от этого напрямую зависит скорость переключения), что с советской элементной базой эта схема вообще бы никогда не заработала в принципе.

Даже по американским меркам потребовалось прецизионное согласование отборных компонентов (первые несколько страниц опубликованной CDC книги о 6600 посвящены тому, как новые кремниевые транзисторы сделали эту машину возможной), потому такая модель и не получила широкого распространения в дальнейшем. Ну и потому, что даже в дискретном варианте грелась как адский котел, в младших моделях – CDC 3000 и 1604 использовалась обычная DTL, хотя и в варианте от Крэя с парой тонкостей.

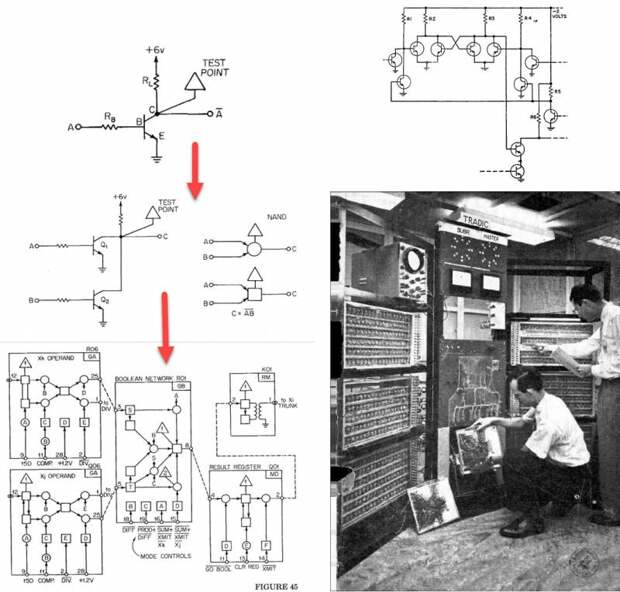

Изобретена DCTL была в Bell Labs еще во время работы над первой транзисторной машиной в истории – TRADIC, законченной в 1954 году. Его версия TRADIC Leprechaun 1956 года использовала как раз DCTL.

Основная идея DCTL проста, как валенок – выкинуть из RTL все резисторы.

Но как тогда переключать транзисторы, не загоняя их слишком далеко в насыщение?

Элементарно: заменить резисторы транзисторами со специальными импедансами и коэффициентами усиления.

Далее следует долгая работа по согласованию всего этого хозяйства. В частности, Крэй рассчитал, что коэффициент усиления насыщенного транзистора должен быть больше, чем удвоенное количество выходных нагрузок, и применительно к CDC 6600 правила таковы: коллектор одного транзистора может управлять пятью базами в пределах модуля или двумя локальными базами в пределах модуля и двумя базами через витую пару на одном другом модуле, и ровно шесть коллекторов могут быть подключены в пределах модуля.

Насколько круты были честные 10 МГц, выжатые из такой схемы?

Для сравнения: частота PDP-8, также на дискретных транзисторах, выпущенного в 1965 году составляла всего 1,5 МГц, и первый IBM PC, выпущенный 20 лет спустя, имел тактовую частоту менее половины от скорости CDC6600, несмотря на то, что был основан на микропроцессоре. За последние лет 20 многие любители электроники возродили как хобби сборку процессоров потранзисторно.

Известны такие любительские компьютеры, как MT15, Megaprocessor или Monster6502, но, несмотря на всю современную элементную базу и знания о новых схемотехнических решениях, возникших за десятилетия, прошедшие с момента создания CDC6600, ни один из современных транзисторных компьютеров не достигает и 1/10 скорости великой машины 1960-х.

Отсюда и кажутся сомнительными цифры в 10 МГц на принципиально иной схемотехнике в БЭСМ-6.

Слева – последовательность сборки логических блоков CDC 6600 из книги Design of a computer the Control Data 6600, справа – схема DCTL-ячейки TRADIC и он сам (https://en.wikipedia.org)

Логическая чистота CDC 6600 тоже была гениальна и минималистична.

Как и во всех своих машинах Крэй построил все на одном-единственном элементе, в данном случае инверторе.

Два инвертора дают AND, еще два + AND дают NOR, на основе NOR собирается все остальное.

Также интересна необычная нотация, примененная Крэем и воспроизведенная в фундаментальной книге Design of a computer the Control Data 6600 написанной вице-президентом лаборатории продвинутого дизайна CDC Джеймсом Торнтоном (James E. Thornton) в 1970 году.

Каждая стрелка соответствует инвертору, круги и квадраты указывают, в какой логике следует интерпретировать текущий узел – положительной (круг) или инвертированной (квадрат). Для обоих вариантов схема абсолютно одинакова. Каждый модуль в CDC 6600 построен из множества базовых инверторов с одним транзистором в каждом. Такой подход был фирменной и узнаваемой идеей Крэя – возьмите только одну самую простую вещь, оптимизируйте до совершенства и соберите на ней все остальное.

В итоге CDC 6600 удалось разогнать до 5 нс – абсолютный рекорд для машин на дискретных транзисторах, который не каждая ECL-микросхема сможет побить. «Эльбрус-2» 1989 года имел скорость переключения вентилей всего в 1,5 раза меньше!

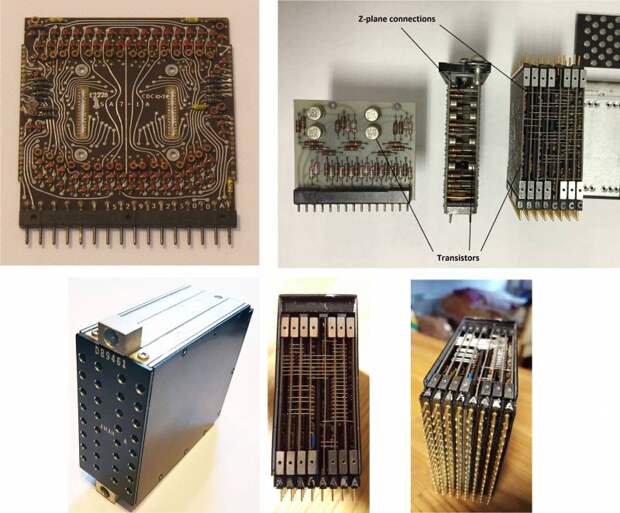

CDC 7600 был построен по аналогичной схеме, только с тотальной миниатюризацией компонентов – каждый ее модуль состоял из 6 или 8 печатных плат, соединенных в cordwood с фреоновой системой охлаждения, а вот CDC 8600 (вопреки гуляющим в интернете байкам) должен был уже быть построен на ECL-микросхемах.

Единственная проблема заключалась в том, что Крэй не смог заставить 4 ее параллельных процессора корректно работать, на доводку требовалось много денег и времени (вообще, технология параллельного программирования в 1960-е была максимально не развита, массово-параллельный ILLIAC IV тоже так и не удалось довести до ума), в итоге он разочаровался в схеме многих процессоров и перешел в Cray-1 (а CDC в STAR-100) к векторной архитектуре.

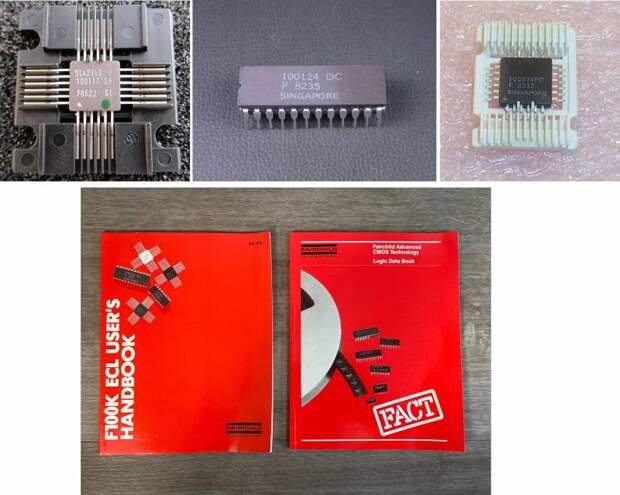

Уникальные фото. Сверху – одна из пластин модуля CDC 7600 и сравнение модулей CDC 6600 и 7600. Снизу – модуль в сборке и вид 6 и 8 пластинных модулей

(https://cds.cern.ch, https://vaxbarn.com, https://people.cs.clemson.edu)

(https://cds.cern.ch, https://vaxbarn.com, https://people.cs.clemson.edu)

Иконой ECL стала Motorola.

В 1962 году они разработали оригинальную топологию, названную скромно и просто – Motorola ECL (MECL).

Первые микросхемы по этой технологии, MC30x/MC35x, выпускались в характерных корпусах-таблетках и имели неплохие параметры: 8–8,5 нс задержка, частота до 30 МГц – вспомним, что СВЧ-транзисторы (ну по тем временам – СВЧ) CDC 6600, выпущенной на 2 года позже, выдавали 10 МГц.

Второе поколение называлось немудрено – MECL II (1966), и ему соответствовали микросхемы MC1000/MC1200 с задержкой 4 нс на вентиль.

Наконец, в 1968 году было разработано третье поколение логики, ставшее таким удачным, что продержалось на конвейере вплоть до середины 1980-х.

MECL III соответствовали микросхемы серии MC16хх, которые, в зависимости от года и типа, работали на частотах от 150 МГц (MC1658 Voltage Controlled Multivibrator) до 1,2 ГГц (MC1699 Divide-by-Four GHz Counter).

В вариантах 1980-х MECL III позволяла проектировать микросхемы до 10 000 вентилей, разогнанные до 0,1–0,2 нс.

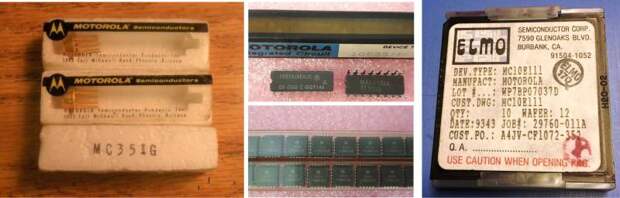

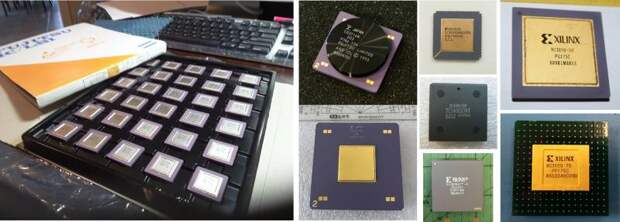

Из запасов ebay – Motorola MC350, MC1000, MC10000 и совсем уж раритет – нераспечатанная упаковка кремниевых пластин для производства их микросхем

(https://www.ebay.com)

(https://www.ebay.com)

В 1971 году Motorola решила сделать небольшое ответвление своей линейки и изготовить чипы, промежуточные между уже немного тормозным MC1000 и космически быстрым MC1600, хотя к этому времени быстродействие MC1000 и выросло в два раза (например, MC1027/MC1227 120 МГц и MC1034/MC1234 180 МГц, при времени задержки в 2 нс, вместо 4 нс у первых экземпляров 1966 года).

Так родилась серия MC10000.

Отличалась она от MECL III только номиналами резисторов, схемотехника была полностью одинаковой.

Первые версии MC10к имели задержки до 2–3 нс и частоту до 125 МГц, а главное – пониженное по сравнению с MECL II/III энергопотребление и тепловыделение. Как всегда, было выпущено 2 серии – военная MC10500 (и MC10600 пораньше) и гражданская MC10100 (и МС10200 попозже).

В линейке нашлось место и такой популярной тогда штуке как BSP – его роль выполнял 4-х битный MC10800.

За этой линейкой последовали MC12k (1976) с частотой 250 МГц и MECL 10H (1981), а в 1987 году появилась ECLinPS (пикосекундная ECL, 0,5 нс) с частотой 1,1 ГГц.

Однако Motorola не стала самым великим производителем американской ECL-логики.

В 1973 году компания Fairchild объявила о выпуске F95K, F10K и F100K.

Эти линейки поразительны сочетанием двух вещей – насколько мало о них знают (даже в англоязычном интернете нет практически ничего, все нужно выколупывать из книг и мануалов) и насколько великие машины на них собирались.

F10K была дальнейшим развитием MC10000 и значительно от нее отличалась.

В связи с непростой судьбой Fairchild в 1970-е (от нее ушли вообще все топовые разработчики и менеджеры, основав всякие Signetics, Intel и AMD, а выпускать чипы было как-то надо), производство F10K зависло на пару лет до 1975 года.

Это была первая в мире полностью скомпенсированная по напряжению питания и температуре ECL-схемотехника, в результате кристалл грелся намного равномернее, а это многократно снижало шумы и температурную нестабильность.

F100K была ультраскоростной версией F10K, разгоняясь до 0,7 нс.

Все линейки собирались по фирменной технологии Isoplanar II, гражданские корпуса были маленькими DIP24. Сама F100K была серией мелкой рассыпухи, ее подтипами стали более крупные F200 (базовые матричные кристаллы для заказных микросхем) и мощнейший 8bit BSP F220 (появилась в 1980, маркировка 10022x).

И аналогичная подборка для Fairchild F100, включая книги разработчика

(https://www.ebay.com)

(https://www.ebay.com)

На таких чипах уже можно стало собрать что-то действительно серьезное, и оно не замедлило появиться – через год после выпуска серии Сеймур Крэй собрал на ней свой великий Cray-1.

Вся машина первой версии была реализована всего на 4 разновидностях микросхем: Fairchild 11C01 (dual OR/NOT), Fairchild 10145A (64-Bit RAM), Fairchild 10415 (1024-Bit RAM) и Motorola MC10009 (более дешевый аналог 11C01 в схемах выборки адреса).

Что интересно, логика была реализована, по сути, на одном типе элементов – 2ИЛИ-НЕ.

Таких микросхем потребовалось 250 000 штук, а микросхем памяти – 65 000 штук.

Естественно, радостью воспользовался не только Крэй, DEC выпустила PDP-10 на SN74LS в 1974 году, а уже через год перевела старшие модели на F10K.

В 1977 году появились улучшенные чипы 4Kbit RAM, и Cray-1 испытал апгрейд памяти.

В те же годы Motorola лицензировала F100K себе обратно и долго мучилась, пытаясь создать аналог, выкатив его только в 1981 году как MC100k (улучшенный клон F200, получил название MCA – Macrocell Array), зато сразу выступила с более широким ассортиментом и затмила оригинал (в результате чего Cray-2 и CDC CYBER собирали уже на ней).

Все 1980-е на архитектуре F100K выпускали кучу всевозможных специализированных и просто мощных машин, включая такую экзотику, как, например, 64-битный вещественный сопроцессор Floating Point Systems FPS-264 (1985), ускорившийся в 5 раз по сравнению с FPS-164 на SN74LS.

IBM начала производство своих ECL-чипов для S/370 с конца 1960-х, не меньше отличились и японцы: Fujitsu разрабатывала оригинальные ECL для себя и Amdahl (и копировала по лицензии F100K), в Европе ECL изготавливала Siemens.

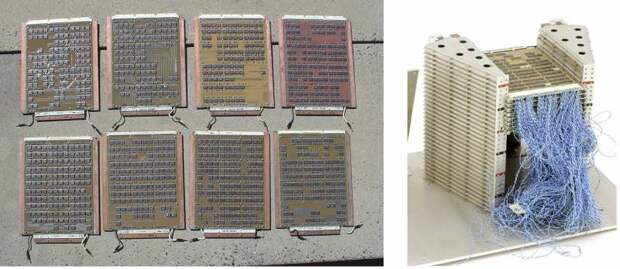

Куча процессорных плат от Cray-1 и принцип их монтажа в охлаждающую стойку

(https://www.digibarn.com/ и https://www.computerhistory.org)

(https://www.digibarn.com/ и https://www.computerhistory.org)

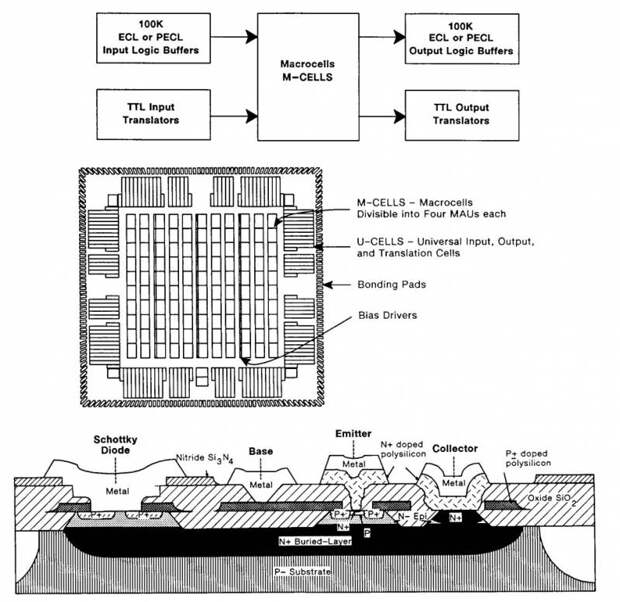

Главной коммерческой серией ECL-БМК второй половины 1980-х стала Motorola MCA3 ETL.

Это были мощные чипы, выполненные по фирменному техпроцессу MOSAIC III со смешанным интерфейсом, поддерживающим ECL, PECL (более продвинутый вариант эмиттерно-связной логики Positive ECL с питанием +5 В) и TTL-чипы. Задержка составляла не более 150 пс, корпуса использовались уже полноценные QFP, PGA и TAB, а вентилей там было от 858 до 6915. Маркировались чипы просто, по количеству доступных вентилей: от MCA600ETL до MCA6500ETL.

Конструкция Motorola MCA 3 из даташита

Высочайшее энергопотребление и тепловыделение ECL означало, что их можно использовать только в системах высшего уровня с жидкостным, иммерсионным или криогенным охлаждением.

В принципе, достаточно медленные чипы могли жить и с воздушным, но в массе своей обычно ставили что-то помощнее.

IBM ES/3900 (кстати, они бухнули около 10 лет и столько же миллиардов на разработку мультичипового модуля TCM – Thermal Conduction Module, для них, фактически именно тогда были изобретены многокристальные процессоры, так популярные в наше время), Amdahl 470/V6, все японские суперкомпьютеры 1980-х, конечно же, Cray-1 и Cray-2, старшие модели DEC от KL10 PDP-10 до VAX 9000 – все они использовали ECL.

Знаменитая серия отказоустойчивых машин Tandem, о которых мы уже писали, в своем сервере TXP (1983) использовала SN74AS, но для своего флагмана NonStop VLX (1986) уже взяла ECL.

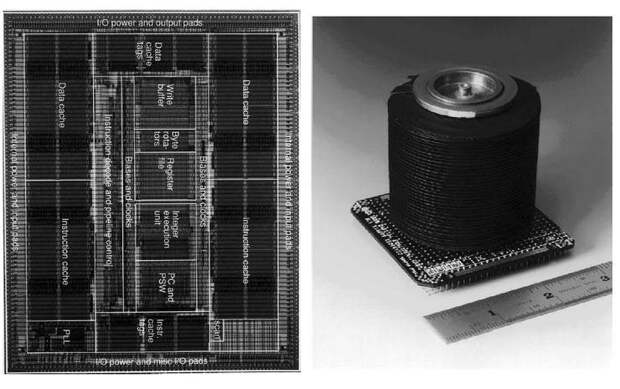

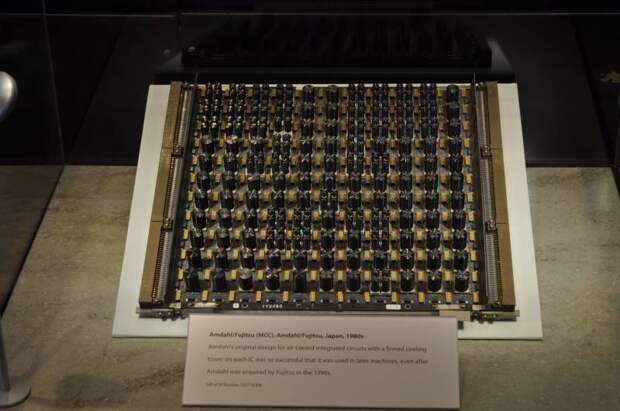

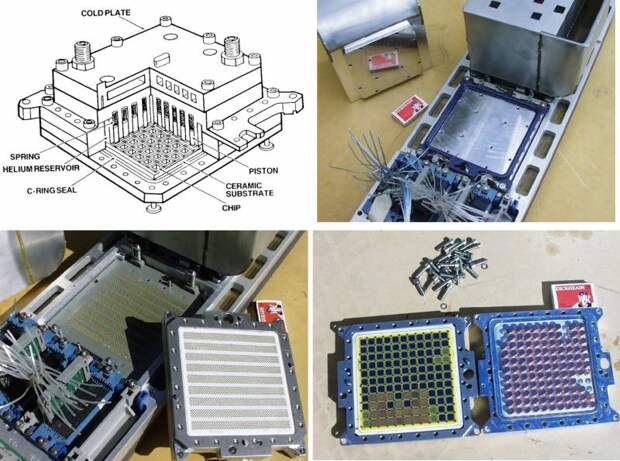

Невероятный TCM – технология, на которую IBM потратила около 10 лет и более миллиарда долларов

(https://www.researchgate.net, http://members.optusnet.com.au)

(https://www.researchgate.net, http://members.optusnet.com.au)

Еще более невероятный процессор мейнфрейма Amdahl 470 и плата от него же производства Fujitsu, все выполнены на ECL БМК. Полностью аналогичную схему использовал мейнфрейм Fujitsu FACOM M-190. На заднем фоне сама машина. Такие платы сейчас стоят среди коллекционеров 2–3 тысячи долларов

(https://i.redd.it, https://www.flickr.com/)

(https://i.redd.it, https://www.flickr.com/)

Еще один клон S/370 – процессор мейнфрейма National Advanced System AS/XL, 1982 года. 8 восьмибитных BSP (клон F220 производства National Semiconductor) образуют 64-битный процессор. Всего для мейнфрейма было разработано порядка 30 заказных микросхем на MECL 10K и MECL 10000 MCA.

Компания DEC в 1984 года попыталась выпустить «убийцу IBM» – мощнейший мейнфрейм VAX 9000.

Компания планировала вложить в разработку примерно миллиард долларов, несмотря на значительную озабоченность сотрудников тем, что RISC-процессоры быстро догоняют многокристальные системы на БМК.

Однако к тому времени PDP-11 еще можно было уместить в однокристальную версию (процессор J-11), классический VAX – уже нет (только его версию MicroVAX 78032).

В 1980 году Джин Амдал создал Trilogy Systems с целью улучшения технологии ECL для своих мейнфреймов, и DEC лицензировала его разработки.

В окончательном варианте процессор VAX 9000 реализовывался как многочиповый модуль по типу IBM, из 13 БМК оригинальной архитектуры, заказанных у Motorola. В процессе разработки в 1988 году IBM выкатила сервер AS/400 (продажи принесли более 14 миллиардов – только на нем одном они подняли денег больше, чем вся DEC), нанеся удар по сегменту VAX.

Одновременно Sun представила свой микропроцессор SPARC, который позволил настольным машинам превзойти даже самые быстрые из существующих машин DEC.

I just don't understand it, I don't see how this is possible, how this one chip can replace these racks of electronics, I just don't get it!

– восклицал несчастный директор DEC Кен Олсен, застрявший, как и советские академики, в 1960-х годах.

Инженеры пытались уговорить его отменить 9000, поясняя, что к моменту выхода он станет не мощнейшим мейнфреймом в мире, а всего лишь обыкновенным сервером, только в 1 000 раз дороже, но Олсен стоял на своем, как наши министры и разработчики.

В итоге DEC вбухала в проект более 3,5 миллиардов и закончила его только к 1990 году, предлагая машину, сравнимую с IBM 3090, по цене около 4 миллионов долларов. Только 40 систем 9000 были произведены и проданы – к тому времени стало очевидно, что CMOS-микропроцессоры взошли на престол навсегда.

В 1991 году появился NVAX – система здорового человека, разработанная группой адекватных инженеров DEC, производительностью с VAX 9000, но в формате обычного микропроцессора.

Он позволил компании не загнуться, но стал последним в славной линейке VAX – на подходе был DECchip 21064, более известный как Alpha, мощнейший и лучший процессор до начала 2000-х.

VAX 9000 стал в каком-то смысле аналогом «Электроника ССБИС» – разработанным на чистом упорстве и глупости, дорогим и бесполезным.

Отличие было лишь в том, что руки инженеров DEC росли из нужных мест (а не как в НИИ «Дельта»), в итоге машина имела воздушное, а не фреоновое охлаждение, была в 20 раз меньше, такая же быстрая, разработка заняла 5 лет, а не 10, и она все-таки дошла до серийного выпуска.

Для сравнения: «Электроника ССБИС», прототип, частично запущенный в том же году, представлял собой набор шкафов с актовый зал, содержащих 5 кило золота, сотни километров разведенного вручную коаксиала, процессор на многослойных бутербродах дискретных плат с фреоновым охлаждением на сотнях ECL-чипов, которые не удалось разогнать даже до паспортных 75 МГц, застряли на 66.

И да, по производительности все это было примерно равно VAX 9000, а на разработку были вбуханы 10 лет, невообразимое количество миллионов и усилия аж целого НИИ «Дельта», толпы престарелых академиков и кучи предприятий.

После такого отечественную микроэлектронику хочется уже пристрелить из жалости, что, в общем-то, в 1991 году и случилось.

Совершенно дивный процессор VAX 9000 на куче БМК. Строго говоря, это не полный процессор в современном смысле слова, машина собиралась из разных модулей, выполненных в таком конструктиве, среди которых были DISTRIBURITON UNIT, INTEGER UNIT, MULTIPLICATION UNIT, FLOATING UNIT, CONTROL UNIT, VIRTUAL INSTRUCTION CACHE, CROSSBAR UNIT, MICRO CONTRO STORAGE и другие. На первой фотографии представлен P1004 FAD (EBOX FLOATING UNIT), назначение следующих техноархеологи еще не выяснили

(фото из коллекции пользователя pixelmanca, https://www.cpu-world.com/forum/)

(фото из коллекции пользователя pixelmanca, https://www.cpu-world.com/forum/)

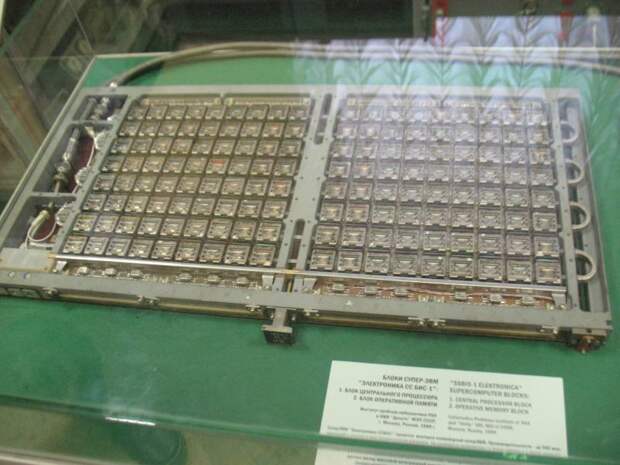

И для сравнения машина, уступающая ему по всем параметрам, но того же года – «Электроника ССБИС».

Фото из коллекции Политехнического музея в Москве (https://1500py470.livejournal.com)

Фото из коллекции Политехнического музея в Москве (https://1500py470.livejournal.com)

ECL в процессорах умерла навсегда, но последним и самым экзотическим ее применением были микропроцессоры!

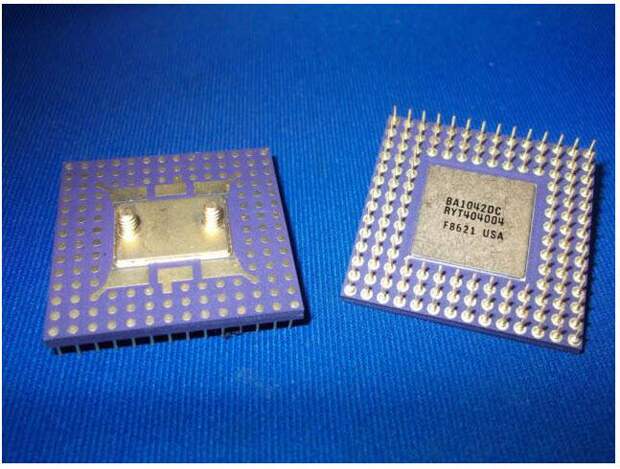

Фирма Bipolar Integrated Technology, крупнейший в начале 1990-х эксперт по биполярной технологии, решила выжать из нее все что можно и нельзя. Они сотрудничали с двумя пионерами RISC – MIPS Computer Systems и Sun Microsystems, чтобы создать на основе RISC архитектур ECL-процессор невиданной мощности.

Первая реализация архитектуры MIPS II – набор чипов R6000, R6010 и R6020, была выполнена в виде MCM-модуля и использовалась в высокопроизводительных серверах Control Data Systems 4680-300 Series InforServer (их пыталась производить бывшая Control Data Corporation, реорганизованная в 1992 году).

Разогнали, кстати, до 80 МГц, и близко не похоже на рекорды, доступные ECL, но зато процессор не прожигал плату насквозь. Для Sun был изготовлен SPARC B5000, информации о котором почти нет.

Наконец, самым безумным чипом на ECL стал экспериментальный микропроцессор от DEC, которые осилили впихнуть MIPS II в один кристалл!

На 1993 год самым мощным микропроцессором общего назначения был Intel Pentium с частотой 66 МГц и TPD 15 Вт. DEC MIPS II имел 300 МГц (!) и 115 Вт (!) – тепловыделение на уровне Core i9. Охлаждению этого монстра была посвящена отдельная статья.

CMOS, однако, покорили такие частоты через 2–3 года при тепловыделении в 3 раза меньшем, и о безумной ECL забыли.

Тот самый монстр DEC MIPS II из статьи 1993 года A 300 MHz 115 W 32 b bipolar ECL microprocessor with on-chip caches в IEEE International Solid-State Circuits Conference Digest of Technical Papers. Фото R6000 и B5000, увы, найти не удалось.

БМК и как его готовить

Перед тем, как перейти к элементной базе «Эльбрус-2», поговорим о том, как вообще на Западе работали с БМК и что это за зверь такой.

1970-е были эпохой сборки процессора из чипов низкой и средней интеграции, что означало, что он представляет собой одну или несколько плат, усыпанных прямоугольниками микросхем (мы говорим, конечно, о процессорах серьезных машин, а не о микропроцессорах).

В 99 % случаев разработкой и изготовлением процессора на всех уровнях занимались сами компании, производящие железо.

С началом 1980-х пришла эпоха LSI и двух новых способов изготовить себе архитектуру.

Во-первых, можно было собрать ее на BSP на любой вкус, скорость и кошеле: от крошечных и медленных TTL Intel 300x до могущественных 8-битных ECL Fairchild F220.

В таком случае изготовление процессора сводилось, по сути, к разработке системы команд и прошивке ее в прилагаемое устройство управления.

Второй метод пригождался, когда архитектура была слишком мощной или концептуальной, чтобы быть воплощенной стандартным способом.

Создатели микросхем довольно быстро поняли, что если предлагать только готовые типовые решения, то можно прозевать клиентов, которые хотят чего-то особенного за дополнительную цену.

Так родилась концепция выпуска заказных чипов на основе того, что в СССР называли БМК, базовые матричные кристаллы, а на Западе – Gate Array.

БМК – это полуготовый чип на ~15–50 000 вентилей, единственное его отличие – то, что большинство транзисторов не имеют заранее определенной функции. Их можно соединить слоями металлизации, образовав стандартные ячейки NAND или NOR, а затем собрать из них полную схему следующим слоем.

Таким образом, чистый БМК существует только в рекламном проспекте или на внутренних складах – все чипы, окончательно выходящие с завода, уже имеют строго заданную структуру.

Мастер-пластины БМК с незаконченными чипами обычно изготавливаются заранее и складируются, в результате проектирование процессора сводится к тому, чтобы накидать в САПР его топологию, а затем пластины поступят далее на конвейер, где эту топологию в них воспроизведут, разрежут, корпусируют и поставят клиенту.

Возможно, кто-то слышал о чем-то подобном, и да, сейчас похожая технология называется application-specific integrated circuit (ASIC).

ASIC – это уже полноценная SoC, включающая, как правило, I/O, контроллеры и память, они применяются в огромном количестве приложений, на них работает куча разнообразного встраиваемого оборудования, а еще, например, майнеры Bitcoin.

Основное отличие в том, что ASIC проектируются из уже сформированных стандартных ячеек, а не голых транзисторов, как БМК.

Конечно же, БМК поставлялись целыми семействами, различающимися количеством вентилей и ценой.

В результате, каждый производитель компьютеров мог подобрать набор микросхем, оптимально ложащихся на его систему команд.

Конечно, есть и тонкости, допустим, перекрестный матричный коммутатор требует гораздо больше соединений и, соответственно, слоев, нежели аналогичный систолический массив, при этом сложность схемы чисто по количеству вентилей будет примерно равной.

Неиспользуемые дорожки и вентили увеличивают сложность и стоимость чипа, как для производителя, так и для заказчика, поэтому великое искусство заключается в том, чтобы спроектировать БМК оптимальным образом, подходящим для большей части применений.

В результате их создатели старались предусмотреть то количество дорожек, которого хватит для маршрутизации большей части топологии, потенциально возможной на таком количестве вентилей.

В этом часто помогает эмпирический закон Рента, открытый одним из инженеров IBM в 1960 году (Rent, E. F.: Microminiature packaging. Logic block to pin ratio. IBM Memoranda, November 28 – December 12 1960). Он гласит, что количество выводов микросхемы равно среднему числу межсоединений, приходящихся на один логический элемент, умноженному на количество логических элементов в степени R, где R – константа Рента (например, для микропроцессоров R = 0,5 – 0,74).

Биполярные массивы были изобретены IBM в 1966 году (IBM Journal of Research and Development Volume: 10, Issue: 5, Sep. 1966). Именно тогда ими была описана технология того, что в будущем назвали полузаказные схемы, а IBM поименовал технологией master slice.

Уже при проектировании S/360 стало очевидно, что следующая машина должна использовать ИС.

IBM никогда ничего ни у кого принципиально не закупала, самостоятельно изготавливая для своих компьютеров все, вплоть до последнего болта.

Естественно, они разработали собственную линейку микросхем, никогда не поступавшую на открытый рынок, и абсолютно оригинальную технологию их изготовления, вплоть до характерных корпусов – не унылых DIP, а узнаваемых металлических кубиков.

Поскольку им требовалось огромное количество чипов, их инженеры нашли способ радикально сократить затраты на производство. Они разработали серию из нескольких кремниевых кристаллов общего назначения, на которые затем наносили металлизацией дорожки, соединяя их в требуемом порядке. Такая болванка и называлась master slice. Для проектирования уже тогда IBM использовали компьютеры.

Fairchild прониклась идеей и выпустила первую в мире коммерческую серию заказных чипов Micromatrix (32-вентильная матрица DTL с задержкой 20 нс) год спустя. В 1968 году вышли два варианта TTL-матриц Polycell (до 144 вентилей, 18 нс).

Одновременно с этим еще три компании анонсировали такие игрушки: Sylvania SL80 (30 вентилей), Motorola (25 и 80 вентилей, 5 нс) и TI Master Slice (несколько ячеек по 16 вентилей).

В 1971 году к празднику присоединилась Raytheon, а в 1973 году они выпустили TTL(S) RA-116, которая производилась до 80-х.

Примерно в это же время крупные производители, такие как RCA и Hughes, тоже вошли в бизнес БМК.

В 1972 британская Ferranti выкатила первую версию своей ULA (Uncommited Logic Array), а позже даже купила американского производителя БМК Interdesign. К 1983 году они дошли до 10000 вентилей на схеме.

CMOS открыла широчайшие возможности производства заказных чипов, первые CMOS-БМК были созданы Робертом Липпом (Robert Lipp) в 1974 году для International Microcircuits, Inc. (IMI).

Технологии САПР в те годы были очень примитивны, поэтому большая часть работ, связанных с проектированием, выполнялась вручную. В 1978 Липп основал конкурента IMI – California Devices, Inc. (CDI).

С 1976 года настала эра расцвета БМК.

На рынок вернулись Fairchild и Motorola со своими ECL и Texas Instruments с I2L и STL.

В Европе БМК занимались как минимум четыре производителя (Ferranti, Philips, Plessey и Siemens), а в Японии наиболее заметными были Fujitsu, Hitachi и NEC.

Программируемые пережигаемыми перемычками FPLA появились в Signetics в 1975 году как результат отработки технологии изготовления нихромовых перемычек используемых в ПЗУ.

В тот же период появились микропроцессоры и разгорелись споры о том, какой вариант развития победит.

Разнообразные заказные чипы и ПЛИС на любой вкус и кошелек, 1985–1995 гг.

(https://www.ebay.com)

(https://www.ebay.com)

БМК на протяжении десяти лет считались серьезными конкурентами микропроцессоров (наверное, процентов 70 больших и средних машин собиралось именно на них), и даже не было предопределено – какой же подход победит.

В 1979 году была основана компания VLSI Technology, как обычно, выходцами из Fairchild Джеком Балетто (Jack Balletto), Дэниэлом Флойдом (Daniel Floyd) и Гуннаром Ветлесеном (Gunnar Wetlesen), в компании с Дугом Фэйрбэрном (Doug Fairbairn) из проекта Xerox PARC.

Компания с самого начала ориентировалась на разработку чипов под заказ, опираясь на интеллектуальные ресурсы близлежащего Калтеха и университета Беркли. VLSI стала первым поставщиком ASIC – заказных микросхем на основе стандартных ячеек в начале 1980-х годов, а вторая компания, LSI Logic, была лидером в производстве микросхем на основе классических БМК.

LSI Logic была создана в 1981 году в той же солнечной Калифорнии и к 1985 году построила совместно с Kawasaki Steel огромный завод по производству пластин в Цукубе (Япония).

В 1983 году по заказу Министерства обороны США была разработана спецификация языка VHDL (VHSIC Hardware Description Language), предназначенного для формального описания логических схем для всех этапов разработки.

В том же году была основана Automated Integrated Design Systems, созданная для разработки САПР микросхем, и разработан их первый продукт – аналог VHDL, язык Verilog.

Компания IBM поспособствовала взлету популярности заказных решений, когда в 1981 году представила свой мощнейший мейнфрейм нового поколения IBM 3081 с процессором, полностью собранным из ECL БМК.

В Великобритании в этот же год на противоположном конце диапазона производительности компания Sinclair создает ZX81 (предшественника иконы домашних ПК – ZX Spectrum) на БМК Ferranti ULA (клонированные в СССР как Т34ВГ1).

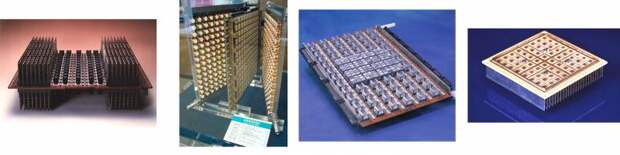

Тяжелый металл по-японски. Это все базовые матричные кристаллы. Fujitsu FACOM M-780 1987 года, мощнейший в мире на тот момент IBM-совместимый мейнфрейм и первый мейнфрейм с процессором на одной плате. Так выглядел бы Ряд-4 здорового и богатого человека. Слева – блок основной памяти из модулей, выполненных вполне по современной технологии, и невообразимый процессор – справа: 54х49 см плата (!) с 336 БМК (!), размещенная бутербродом между двух охлаждающих пластин с индивидуальными медными стержнями-теплоотводами к каждому кристаллу. Далее: NEC и Hitachi тоже имели чудовищные платы, процессор Hitachi HITAC M-68X (1986) и NEC ACOS System 1000 (1980)

(http://museum.ipsj.or.jp)

(http://museum.ipsj.or.jp)

Далее рынок уже было не остановить.

В 1983 году возникает компания Altera, предлагая на рынке принципиальную новинку – реконфигурируемый программируемый пользователем чип EP300.

В 1985 Росс Фриман (Ross Freeman) и Бернард Вондершмидт (Bernard Vonderschmitt) изобретают и патентуют новый способ создания таких матриц, названных field-programmable gate array (FPGA).

С выпуска в том же году первой FPGA XC2064 начинается история главного конкурента Altera – компании Xilinx.

Ее первые продукты были во многом похожи на ранние БМК – медленные и дорогие, пригодные только для некоторых нишевых рынков. Однако закон Мура быстро сделал их силой, и к началу 1990-х годов они серьезно подорвали рынок заказных микросхем.

Наконец, в 1988 году была основана Cadence Design Systems – компания, продвинувшая автоматизированную разработку чипов на новый уровень и сейчас предлагающая системы проектирования, лицензируемые за миллионы долларов.

Практически все современные микропроцессоры от Intel Core i9 до Apple M1 созданы в САПР Cadence. Классические БМК вымерли к середине 1990-х, вытесненные FPGA, ASIC и микропроцессорами, но их влияние на развитие компьютеров было колоссальным.

Итак, как выглядела разработка заказной ECL-микросхемы на БМК Fairchild F200 в 1981 году?

Обратимся к рекламному проспекту самой компании.

Используя самое быстрое семейство ECL для своего БМК F200, компания Fairchild сохраняет совместимость с F100K.

Разработка ведется почти полностью на компьютере.

Fairchild взимает вступительный взнос в размере от $20 000 до $25 000 и предоставляет обучение (от 2 до 8 недель) по использованию нашей компьютерной сети Cybernet.

Создание БМК с использованием макрофункциональных ячеек выполняется вручную, но на следующих этапах (генерация тестовых векторов и проверка проекта) используется программа TEGAS на Cybernet.

Соединение и размещение макросов частично выполняется вручную, частично с помощью компьютера; проверка правил проектирования выполняется компьютером.

Плата за компьютерное время составляет от $5 000 до $15 000, в прямой зависимости от уровня вашего опыта.

Изготовление базовой маски для массива F200 стоит от $10 000 до $15 000; Fairchild также выполнит проектирование и компоновку за дополнительные $25 000–30 000 (теперь вы знаете, почему мейнфреймы стоят недешево).

Разработка ведется почти полностью на компьютере.

Fairchild взимает вступительный взнос в размере от $20 000 до $25 000 и предоставляет обучение (от 2 до 8 недель) по использованию нашей компьютерной сети Cybernet.

Создание БМК с использованием макрофункциональных ячеек выполняется вручную, но на следующих этапах (генерация тестовых векторов и проверка проекта) используется программа TEGAS на Cybernet.

Соединение и размещение макросов частично выполняется вручную, частично с помощью компьютера; проверка правил проектирования выполняется компьютером.

Плата за компьютерное время составляет от $5 000 до $15 000, в прямой зависимости от уровня вашего опыта.

Изготовление базовой маски для массива F200 стоит от $10 000 до $15 000; Fairchild также выполнит проектирование и компоновку за дополнительные $25 000–30 000 (теперь вы знаете, почему мейнфреймы стоят недешево).

Fairchild F300 FGA2000 – мощный БМК 1980-х годов, мечта советских разработчиков

(https://1500py470.livejournal.com)

(https://1500py470.livejournal.com)

Как видите, использование технологии БМК требует значительных затрат времени и ресурсов; вы должны сотрудничать с производителем кристалла для создания схем системной логики, последовательностей функциональных тестов, преобразования логики в шаблоны вентильных матриц, моделирования программного и аппаратного обеспечения, диаграмм межсоединений, разработки масок и изготовления прототипов.

В СССР все это легло на плечи отдельных институтов, коих насчитывалось три, и они были конкурентами: ИТМиВТ («Эльбрус-2» второго поколения), НИЦЭВТ (ЕС ЭВМ Ряд-4) и НИИ «Дельта» («Электроника ССБИС»).

ИТМиВТ и НИЦЭВТ принадлежали к МРП, а «Дельта» – к МЭП, причем 90 % заводов по производству микросхем владел именно МЭП.

Пока был жив друг Шокина Калмыков – проблем для МРП это не составляло. Со сменой же министра на Плешакова в 1974 году процесс сотрудничества затормозился.

Дополнительно ситуацию ухудшили интриги между тремя группами разработчиков – Пржиялковским с ЕС ЭВМ и Бурцевым с «Эльбрус-2» внутри МРП, и Мельниковым с «Электроника ССБИС» из МЭП.

МЭП тоже захотел свой суперкомпьютер и, изгнав в него в 1974 Мельникова, Бурцев создал себе опасного конкурента.

В начале 1980-х был принят проект «Электроника ССБИС», для которого тоже были нужны БМК, и в самый критический для «Эльбруса-2» период сотрудничество МРП и МЭП повисло на волоске.

Пришлось идти на поклон к внутренним конкурентам – НИЦЭВТ в их знаменитую штаб-квартиру, 700-метровый «лежачий небоскреб» на Варшавском, самое длинное научное здание в мире. В этом небоскребе в соседних комнатах сотрудники НИЦЭВТ и ИТМиВТ совместно колупали тему БМК.

Неудивительно, что разработка БМК занимала в Союзе несколько лет.

Даже в США, на родине технологии, где она была досконально изучена с самого начала и где микроэлектронный бизнес работал в те годы просто на пределе человеческого КПД (с учетом, какие безумные, невообразимые деньги там крутились), полный цикл проектирования БМК занимал в 1980-е годф от 6 до 12 месяцев.

Превосходили американцев в то время только японцы, которые работали уже на пределе не человеческого, а КПД биороботов, поэтому 4 гиганта – Fujitsu, NEC, Toshiba и Hitachi (и мудро заказавшая у японцев из Fujitsu БМК компания Amdahl) рвали американский рынок в клочья, пока не вмешался Рейган с протективными мерами (и пока IBM грязно не засудила Джина Амдала за то, что дерзнул выпустить машину, совместимую с S/370, но в два раза лучше).

Если же учесть, что каждая схема требовала, как правило, несколько итераций для оттачивания архитектуры, а ценой ничтожной ошибки становилась запоротая партия в тысячи чипов – неудивительно, что работать с БМК могли себе позволить только очень-очень толстые компании для очень солидных проектов.

В результате задержки между анонсированием новой технологии БМК и реальными машинами на них составляли 3–4 года даже в случае США – на самом деле при всем качестве советских микросхем, просто чудо и подвиг, что их осилили выпустить за 6–7 лет.

Чудовищно богатая Fujitsu со штатом в тысячи инженеров и полным циклом производства могла позволить себе выпустить мейнфрейм для Amdahl в 1980 году на БМК на 10К вентилей, а разработка усилиями нескольких человек суперкомпьютера Cray X-MP на крошечных по сравнению с Fujitsu всего-то 16-вентильных матрицах завершилась только в 1982 году.

CDC писала в рекламе:

CDC использует самое быстрое для своего времени семейство ECL Fairchild F200, совместимых с серией Fairchild F100K, чтобы было возможно совместное использование этих БМК и стандартных схем с целью уменьшить число требуемых вариантов.

Проектирование с использованием F200 очень дорогостоящие.

Разработка почти полностью выполняется на арендном компьютере, стоящим у Fairchild через терминалы у заказчиков.

Проектирование с использованием F200 очень дорогостоящие.

Разработка почти полностью выполняется на арендном компьютере, стоящим у Fairchild через терминалы у заказчиков.

Возникает резонный вопрос.

Компании CDC и Cray находились буквально на пике технического прогресса 1980–1990 годов, будучи крошечными по штату, они умудрялись выживать в обществе толпящихся вокруг гигантов Fujitsu, IBM и UNISYS. При этом они производили ЭВМ вручную, и количество каждой модели исчислялось всего десятками штук.

Бизнес их шел всегда, хромая на обе ноги, как вообще они выживали-то?

И откуда раз за разом брали сумасшедшие деньги на разработку, по прибыли вечно выходя почти в ноль?

И почему при всех талантах их инженеров эта схема внезапно перестала работать в 1990 году?

У ответа на этот вопрос есть имя.

Рональд Уилсон Рейган.

Как мы уже упоминали, 1970-е были золотым веком советских партократов.

Продолжающаяся разрядка, нефтедоллары, техническое сотрудничество с США. Впервые с конца 1950-х наших людей снова стали пускать на Motorola, дошло до того, что в 1975–1976 годы вполне продуктивно шли переговоры с IBM о нормальном лицензировании ЕС (с учетом, что этим уже был и так занят весь мир – и немцы, и британцы, и японцы), а на Motorola мы легально закупали пачками MC10k.

Однако процесс затянулся на пару лет, а потом случились непредвиденные события, поставившие на всех планах жирный крест. Афганистан, восстание «Солидарности» в Польше и военное положение в ней а, как вишенка на торте – смерть Брежнева и приход к власти «мини-Сталина» – Андропова.

Рейган, естественно, использовал все это как casus belli, и последовал финальный мощнейший виток холодной войны, добивший СССР за 10 лет.

Правительство США инвестировало за это десятилетие максимальную со времен Второй мировой войны сумму в разнообразные НИОКР двойного назначения, что привело к невероятному буйному расцвету именно в 1980-е самых странных, экзотических и уникальных архитектур и машин.

А с 1990 года необходимость во вливании средств отпала, и рынок остался решать судьбы всего, что напридумывали в жирное десятилетие.

Как мы знаем, он и порешал: за следующие 5 лет в конкурентной борьбе победили RISC-микропроцессоры и массово-параллельная архитектура на них, вытеснившая весь дивный зоопарк.

CDC получала прямые инвестиции от правительства с ухода из нее Крэя в 1972 году, и это позволило ей все-таки закончить полностью убыточный STAR-100, в проектирование которого были колоссальные трудности (с учетом того, что одна связь с управляющим компьютером PDP-11 там была реализована на аж 4 видах ECL БМК по 168 вентилей каждая).

На самом деле весть проект STAR был ширмой для разработки трех систем: Flexible Processor (FP), Image Processor (IP) и Advanced Flexible Processor (AFP), также известный как Cyberplus, предназначенных для обработки фотоизображений и радиолокационных данных для ЦРУ и АНБ.

К 1986 года по меньшей мере 21 многопроцессорная установка Cyberplus на заказных микросхемах была инсталлирована. Эти системы параллельной обработки включали от 1 до 256 процессоров Cyberplus, обеспечивающих 250 MFLOPS каждый, которые подключены к машинам CYBER через архитектуру прямого подключения памяти (MIA).

Количество выпущенных и установленных FP и IP неизвестно, последним военным продуктом CDC стал Parallel Modular Signal Processor (PMSP), выпущенный в 1988 году.

Так что развитие БМК на ECL было щедро оплачено американским правительством.

Вообще, в США было выпущено невероятное количество секретных архитектур, в основном для АНБ и ЦРУ, многие криптокомпьютеры засекречены до сих пор.

Например, в National Cryptologic Museum демонстрируется некая плата на MC100k под названием CLAW 1 и говорится, что она была инсталлирована аж в CDC 7600(!), но как и главное – зачем, никому не известно, и информации о ней нет.

Архитектура Advanced Flexible Processor и таинственная плата CLAW 1 на натуральной ECL от Motorola

(https://1500py470.livejournal.com, https://en.wikipedia.org)

(https://1500py470.livejournal.com, https://en.wikipedia.org)

В это время в СССР

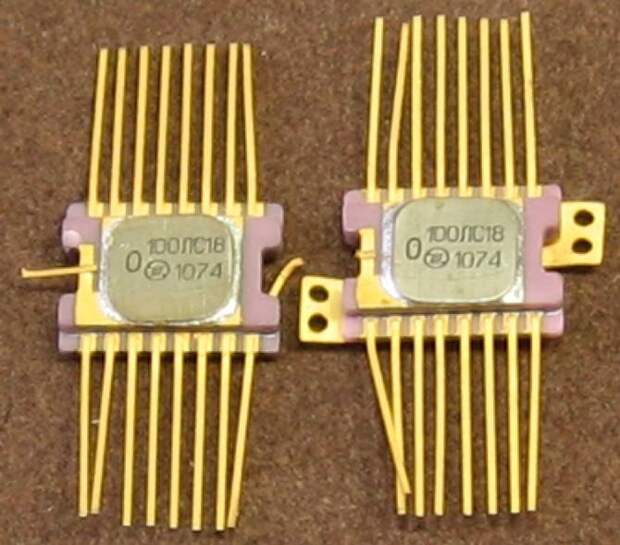

В СССР история ECL началась, кто бы сомневался, с той же Motorola.

У нас иногда случаются упоминания о том, что переход на копирование БМК серии 10k, как обычно, загубил уникальные советские разработки, представленные в конце 1960-х сериями 137, 187, 229 и 138.

Вспоминает наш любимый Малашевич:

Интересный пример – создание ЭСЛ ИС серии 100.

Еще к 1969 г. в НИИМЭ была разработана, поставлена на Микроне своя технология производства ЭСЛ ИС и получены первые образцы нескольких оригинальных ИС серии 138.

Но вскоре началась разработка суперЭВМ «Эльбрус», и по требованию ее главного конструктора (подкрепленного постановлением ЦК КПСС и СМ СССР, с которым не поспоришь) НИИМЭ и Микрону было поручено воспроизведение серии МС10000 фирмы Motorola.

Выпускать две близкие по характеристикам серии ИС было и не целесообразно, и не по силам НИИМЭ и Микрону.

В результате развитие оригинальной серии К138 пришлось остановить и, в угоду заказчику, делать аналоги уже давно выпускаемых МС10000 (серия 100), уступающих серии К138 по быстродействию (важнейший для ЭСЛ ИС параметр).

Еще к 1969 г. в НИИМЭ была разработана, поставлена на Микроне своя технология производства ЭСЛ ИС и получены первые образцы нескольких оригинальных ИС серии 138.

Но вскоре началась разработка суперЭВМ «Эльбрус», и по требованию ее главного конструктора (подкрепленного постановлением ЦК КПСС и СМ СССР, с которым не поспоришь) НИИМЭ и Микрону было поручено воспроизведение серии МС10000 фирмы Motorola.

Выпускать две близкие по характеристикам серии ИС было и не целесообразно, и не по силам НИИМЭ и Микрону.

В результате развитие оригинальной серии К138 пришлось остановить и, в угоду заказчику, делать аналоги уже давно выпускаемых МС10000 (серия 100), уступающих серии К138 по быстродействию (важнейший для ЭСЛ ИС параметр).

На самом деле тут, как обычно, все так да не так.

Собственно, сразу же с основанием Зеленограда в нем (по мере запуска новых заводов и строительства новых НИИ) разворачивали все новые и новые линии копирования. Вместе с TTL и DTL с середины 1960-х начинается колупание и ECL-чипов.

Самые первые советские ECL – раритетная серия Д34 и Д35, прототип, появившийся в 1968 году и являющий собой точный клон Motorola MECL-I. Спустя год вышла их чуть усовершенствованная версия – 137-ая серия (в планарном золотом корпусе для военных известная, как 191).

Изначально их разрабатывали по заказу Пржиялковского из НИЦЭВТ для сборки флагмана первого ряда ЕС – ЕС-1050. Она имела трехстадийный асинхронный конвейер и производительность в 500 MIPS, в принципе, неплохо.

Флагманом вообще должна была стать ЕС-1060, но ее изготовить не успели и перенесли в Ряд-2.

Коллектив под разработку машины Р-500, позже ставшей известной как ЕС-1050, был сформирован в 1968 году (всего изначально хотели сделать 4 варианта: Р-20, Р-100, Р-500 и Р-2000), в том же году началась разработка 137-й серии.

Вспоминает Юрий Ломов, участник разработки ЕС-1050:

...Элементная база (интегральные логические схемы средней интеграции ECL137, ECL138 и ферритовые сердечники в качестве элементов памяти), хотя и значительно уступала зарубежной, всё же позволяла реализовать предложенную архитектуру ЭВМ.

Так что с выполнением требований по производительности (500 тыс. оп/с) с точки зрения возможностей архитектуры у нас трудностей не ожидалось.

Так что с выполнением требований по производительности (500 тыс. оп/с) с точки зрения возможностей архитектуры у нас трудностей не ожидалось.

В итоге 137-я серия была клоном MECL I 1962 года, а 138-я (со временем задержки 3 нс) – клоном MECL II.

В планарном корпусе это, соответственно, 191/197 серии, 229 серия гибридный аналог, 187-я – более медленный и холодный вариант 137-й. С учетом, что ЕС-1050 сдали только в 1974 году, на 1970–1971 не факт, что вообще был налажен их серийный выпуск.

Как мы видим, Борис Малашевич, мягко говоря, заблуждается, во-первых, это и близко не оригинальные чипы, во-вторых, их параметры значительно уступают как MECL III, так и MC10000, и «Эльбрус-2» (потенциально планируемый на 1975–1978 годы) на них собирать смысла никакого не было.

Третья ошибка заключается в том, что их якобы сняли с производства по приказу ИТМиВТ и загнобили передовые разработки. На 137/138 серии успешно собирались и ЕС-1050 и 1052, вплоть до 1980 года, всего было выпушено около 170 машин.

В принципе, их выпуск обеспечил стабильные заказы на 137-ю серию на ближайшие 10 лет, а использовать ее в «Эльбрусе» никто бы и не подумал, слишком тормозная и не для того и создавалась.

Что забавно, в ЕС-1060 использовалась уже не только К500, но и ее оригинал – настоящая живая Motorola MC10k! Вспоминает Ломов, тогда уже ведущий разработчик ЕС-1060:

...У ЭВМ ЕС-1060 начало разработки 1972 год, а окончание – 1977 год.

Элементная база интегральные логические схемы средней серии К500, которую породили отходы от 100 и 700 серии, создаваемой для «Эльбрусов» из ИТМиВТ.

Основную сложность при разработке создавало отсутствие в тот момент интегральных схем статической памяти для буферных памятей процессора и каналов, а также интегральных схем динамической памяти для ОЗУ.

ИС статической памяти на опытный образец и первые серийные образцы пришлось закупать за рубежом.

Элементная база интегральные логические схемы средней серии К500, которую породили отходы от 100 и 700 серии, создаваемой для «Эльбрусов» из ИТМиВТ.

Основную сложность при разработке создавало отсутствие в тот момент интегральных схем статической памяти для буферных памятей процессора и каналов, а также интегральных схем динамической памяти для ОЗУ.

ИС статической памяти на опытный образец и первые серийные образцы пришлось закупать за рубежом.

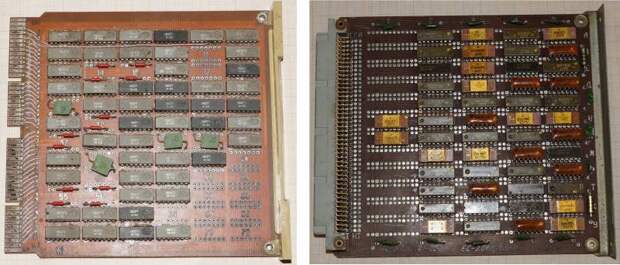

Два процессорнных ТЭЗ-а от ЕС ЭВМ. Слева – ЕС-1050 на ECL-серии 137, справа – ЕС-1060 на ECL-серии К500. Обратите внимание, что на второй советские микросхемы спокойно соседствуют с их оригиналом – Motorola MC10k

(https://1500py470.livejournal.com)

(https://1500py470.livejournal.com)

Многократно поминаемый Малашевич (коренной мэповец) пишет:

О сроках создания ЭСЛ ИС.

Е. Горнев утверждает, что когда К. А. Валиев был в США (1973 или 1974 год), работа по микросхемам ЭСЛ только начиналась (с 1974 года), и никакой серии 500 (а вернее, К500) еще не было.

Ее производство было начато в конце 70-х годов.

Е. Горнев утверждает, что когда К. А. Валиев был в США (1973 или 1974 год), работа по микросхемам ЭСЛ только начиналась (с 1974 года), и никакой серии 500 (а вернее, К500) еще не было.

Ее производство было начато в конце 70-х годов.

Впрочем, техноархеологи легко опровергли эти фантазии (из блога):

Я переговорил с непосредственными участниками тех событий – Н. Лукановым, С. Назаровым, О. Бочкиным, Ю. Журавлевым, причем первые двое руководили темами по ЭСЛ-приборам.

По их общему мнению, в то время Горнев никакого отношения к ЭСЛ-тематике не имел. Выяснилось следующее:

Работы по ЭСЛ-технологии в НИИМЭ были начаты не в 1974 г., а гораздо ранее.

Уже в 1969 г. были получены первые ЭСЛ-схемы (Г. Красников, упомянутый сборник «НИИМЭ – Микрон»)…

К моменту визита К. Валиева и В. Колесникова в США были готовы шесть типов ИС, их большую упаковку с ИС серии 500 в пластмассовых корпусах и показали в Motorola (Н. Луканов, упомянутый сборник «Микроэлектроника»).

Сам факт этого визита и сравнения ИС подтверждается интервью Валиева к 40-летию НИИМЭ, в котором он сказал:

«С собой мы привезли образцы ИС высокоскоростных серий. И когда американцы сравнили их со своими, оказалось, что они практически полностью взаимозаменяемы. Получается, что в то время мы шли, как говорится, ноздря в ноздрю».

В рассматриваемый период я работал в СВЦ, где в 1972–1973 годы на основе микроновских ЭСЛ ИС серии 100 разрабатывался эскизный проект супер-ЭВМ 41-50, образцы ИС у нас уже были.

Из этого следует, что по вопросу ЭСЛ ИС информация Е. Горнева полностью ошибочна.

По их общему мнению, в то время Горнев никакого отношения к ЭСЛ-тематике не имел. Выяснилось следующее:

Работы по ЭСЛ-технологии в НИИМЭ были начаты не в 1974 г., а гораздо ранее.

Уже в 1969 г. были получены первые ЭСЛ-схемы (Г. Красников, упомянутый сборник «НИИМЭ – Микрон»)…

К моменту визита К. Валиева и В. Колесникова в США были готовы шесть типов ИС, их большую упаковку с ИС серии 500 в пластмассовых корпусах и показали в Motorola (Н. Луканов, упомянутый сборник «Микроэлектроника»).

Сам факт этого визита и сравнения ИС подтверждается интервью Валиева к 40-летию НИИМЭ, в котором он сказал:

«С собой мы привезли образцы ИС высокоскоростных серий. И когда американцы сравнили их со своими, оказалось, что они практически полностью взаимозаменяемы. Получается, что в то время мы шли, как говорится, ноздря в ноздрю».

В рассматриваемый период я работал в СВЦ, где в 1972–1973 годы на основе микроновских ЭСЛ ИС серии 100 разрабатывался эскизный проект супер-ЭВМ 41-50, образцы ИС у нас уже были.

Из этого следует, что по вопросу ЭСЛ ИС информация Е. Горнева полностью ошибочна.

Ноздря в ноздрю – это, конечно же, знатное преувеличение.

В итоге к 1975 году промышленный выпуск 100, 500 и 700-й серий был все-таки налажен, но не без великих косяков.

Технически это были одни и те же чипы, только 100-я серия делалась в планарном военном исполнении, 500-я – в гражданском DIP, а 700-я была спецзаказом ИТМиВТ – бескорпусные 100-е для размещения в микросборках К200, по 8–10 микросхем.

Этот заказ был размещен в 1972 году, так как Бурцев считал, что использование микросборок поднимет скорость (не забывайте, магией настоящих мультичиповых модулей тогда владел лишь IBM).

Почему для визита Валиева и Колесникова в США были приготовлены К500?

Не по причине секретности 100-й серии, а потому что в ней мы поначалу сдуру изменили выводы питания, разведя их по углам корпуса.

Казалось бы, ерунда?

Да, но не тогда, когда шла речь о наносекундных ИС.

Из-за такого расположения увеличилась длина проводников и незначительно изменилась индуктивность, чего хватило для того, чтобы помехозащищенность сотки была намного хуже, чем оригинала, а все мы знаем, как чувствительна ECL к помехам.

Показывать их – было бы только позориться, обнажая свое невежество.

Вот она, сотая серия, основа «Эльбруса-2»

(https://1500py470.livejournal.com)

(https://1500py470.livejournal.com)

Далее янки забили улучшать технологию МС10000, потому как появилась новая серия МС10100, а с ней, как видно на ТЭЗ из ЕС-1060, процесс копирования шёл тяжко.

Скопировать К500ТМ130 осилили, а ТМ133 ещё нет, а с памятью MC10400 вообще получилось так плохо, что американские чипы пришлось аж ставить на серийные машины в первый год выпуска.

Американцы же уже выпустили MC10200…

На самом деле идея ЕС, как мы уже говорили, была сама по себе хорошей, да и конструкторы у нас постарались, подвела элементная база.

Серия Ряд-1 ЕС в итоге в целом была довольно балованной (из-за скверного изготовления гражданской TTL), а вот с ЕС-1060 изначально вышла просто катастрофа.

Например, в том же НИИ «Дельта» Мельникова расчеты для «Электроника ССБИС» предпочитали делать по классике – на БЭСМ-6, до тех пор пока их ЕС-1060 не заменили на гэдээровскую ЕС-1055М, причем ненависть к ЕС Мельников в итоге сохранил на всю жизнь.

Впрочем, МЭП выкрутился легко – выпустил свои собственные ТУ, которые не совпадали с ТХ в тех параметрах, которые не удалось выдержать, и 500-ка спокойно прошла приемку, пользуясь неограниченным покровительством повелителя клонов Шокина.

Дело кончилось тем, что непосредственно к Шокину пришли представители Министерства обороны (которым тоже была нужна мощная ЕС в качестве компьютера общего назначения, а не спецвычислителей ПВО/ПРО) и выказали свое официальное недовольство следующими фактами.

В К500, как оказалось, начисто отсутствовали термокомпенсирующие цепи, в результате чего ЕС-1060 мгновенно разогревалась до 70+ градусов, причем это был единственный способ обеспечить ее хоть какую-то работоспособность, т. к. при равномерном нагреве она работала (хотя и безбожно тормозя), а при неравномерном – начинала чудовищно глючить из-за рассинхронизации между более холодными и более горячими ИС.

В итоге при температурном диапазоне, предусмотренном руководящими документами МО, микросхемы не работали, о чем и была высказана претензия.

Однако Шокин (который впадал в неописуемую ярость, если считал, что кто-то смеет с ним не соглашаться) показал, что Министерство обороны для МЭП не указ.

По словам очевидцев, он таким могучим крестьянским великорусским языком объяснил, что МЭП изготовило 500-ю серию в полном соответствии со своими ТУ, а ТЗ от МО может отправляться прямо и налево, что были шокированы даже военные, и они ретировались из кабинета.

В итоге окончательно проклятую серию 100/500/700 допринимали только к 1980 году и заодно вылечили ее детские болячки.

Неудивительно, что одним из первых указов Горбачева, которыми он начал расчищать авгиевы конюшни советских министерств, стал указ об отставке Шокина.

Впрочем, официально выпнуть его он не успел, тот понял, что запахло жареным, и предпочел чуть раньше уйти сам.

Собственно, об этом вспоминает и Бурцев:

МВК «Эльбрус-2» строился уже на новой элементной базе.

Это вызвало массу проблем.

ИС оказались чрезвычайно ненадежными: поскольку их копировали, многое не докопировали, были системные ошибки.

Мы целый год стояли, не зная, что делать, особенно с памятью.

МЭП разместило производство ИС на разных заводах, и мне пришлось организовывать входной контроль, потому что, например, зеленоградские схемы (завод «Микрон») работали прекрасно, а у ИС, произведенных в Каунасе, происходила разгерметизация корпуса.

Это вызвало массу проблем.

ИС оказались чрезвычайно ненадежными: поскольку их копировали, многое не докопировали, были системные ошибки.

Мы целый год стояли, не зная, что делать, особенно с памятью.

МЭП разместило производство ИС на разных заводах, и мне пришлось организовывать входной контроль, потому что, например, зеленоградские схемы (завод «Микрон») работали прекрасно, а у ИС, произведенных в Каунасе, происходила разгерметизация корпуса.

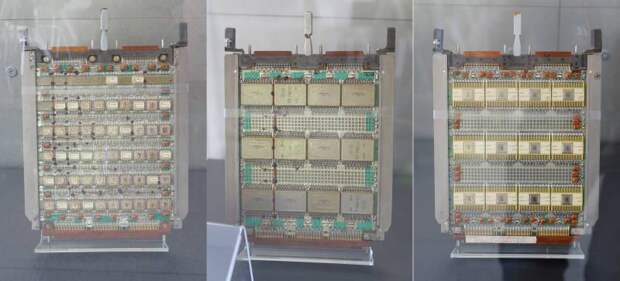

Платы от «Эльбруса-2» двух поколений. Сначала на 100-й серии и сборках К200 из 10 таких кристаллов, а потом на БМК И200. Платы выставлены в Маунтин-Вью в Калифорнии

(https://1500py470.livejournal.com)

(https://1500py470.livejournal.com)

Максимальные проблемы поджидали, как несложно догадаться, с К200 – попыткой изобразить советский MCM а-ля IBM 3081.

Многие инженеры, работавшие в ИТМиВТ, считали решение Бурцева о возне с МБИС (многокристальные БИС, не путать с дальнейшими МаБИС – матричными БИС, т. е. БМК серии И200!) совершенно ошибочным и дополнительно задержавшим работы по «Эльбрусу-2».

Первые К200 были готовы в 1976 году, и началась разработка процессора.

Примерно половина его логики была реализована в виде отдельных микросхем 100-й серии, а другая половина – в виде модулей К200.

Установка корпусирования была изготовлена в самом ИТМиВТ, и лучше бы они этого не делали…

Отладка началась только к 1981 году, по одной из оценок, надежность сборок была такова, что при каждом включении и выключении в процессоре что-то сгорало.

В день заменяли до 5 ТЭЗ, из-за этого отладка заняла в три раза больше времени, чем планировали.

В общем-то, с TTL в «Эльбрусе-1» ситуация была не сильно лучше.

В итоге к 1984 году машина была de jure сдана, de facto же это был прототип, который еще шлифовать и шлифовать (как мы знаем дошлифовали только к 1989 году, еще раз сменив элементную базу, а в полноценную серию она пошла только с 1990 году).

В результате Бурцев на 10 лет профукал все мыслимые сроки сдачи (при том, что эрзац-Эльбрус, первая версия на TTL, тоже нормально заработал не ранее начала 1980-х, и для такого дикого вливания денег и надрыва сил получился совсем уж убогим).

Именно это и дало недоброжелателям Бурцева совершить революцию в ИТМиВТ и, пользуясь тем, что его могучий патрон Калмыков уже 10 лет как был в могиле, повторить над ним то же, что Бурцев проделал со Старосом.

Еще до сдачи «Эльбруса-2» стало ясно, что он, как и его первая версия, безнадежно устарел технически.

Серия MC10k неплохо выглядела в 1970-м, но к 1985 году была уже музейным металлоломом.

Как мы уже упоминали, претендентов на новые технологии в СССР хватало.

НИИ «Дельта» – со стороны МЭП и ИТМиВТ с НИЦЭВТ – со стороны МРП, при этом на первом этапе производили и разрабатывали все типы ECL только в Зеленограде на заводах МЭП.

- Автор:

- Алексей Ерёменко

- Использованы фотографии:

- http://www.righto.com, https://www.computerhistory.org, https://1500py470.livejournal.com, http://ibm-1401.info, http://ummr.altervista.org/, https://www.ebay.com, https://www.digibarn.com/, https://i.redd.it, https://www.flickr.com/, https://www.cpu-world.com/forum/, https://www.cpu-world.com/forum/, http://museum.ipsj.or.jp, http://www.retrocomputingtasmania.com, https://vak.dreamwidth.org/, https://en.wikipedia.org, https://cds.cern.ch, https://vaxbarn.com, https://people.cs.clemson.edu, https://en.wikipedia.org

Свежие комментарии